-

SK하이닉스 소개 및 공정 정리, 팁 1편_200607취준시 소소한 팁 2020. 6. 7. 16:24

SK하이닉스 소개 및 공정 정리, 팁 (made by 슬루리)입니다.

실제로 제가 면접 준비하면서 준비했던 자료구요. 저 혼자 만들었습니다.

2019년 기준 자료이므로 약간 오래된 면이 있습니다.

참고하시어 SK하이닉스 면접을 잘 마무리 하셨으면 좋겠습니다.

출처 : https://blog.skhynix.com/ + 하이닉스 홈페이지

1. SK하이닉스 소개

SK하이닉스는 SK그룹 내 반도체 제품을 만드는 회사로 메모리 반도체, 시스템 반도체 제품을 만든다. SK하이닉스는 메모리 반도체에서 D램, NAND 제품, 시스템 반도체 IMAGE 제품을 주력으로 생산한다.

SK하이닉스는 2018년 기준 매출액 40.44조원, 영업이익 20.84조원을 기록했다. 이는 사상 최대 경영 실적으로 영업이익률이 ‘52%’다. 인사담당자는 “SK하이닉스는 반도체의 상품기획, 소자, 설계, 공정, 제품, 판매 처음부터 끝까지 하는 회사다”라며 “메모리가 안 쓰이는 제품이 없다. 그만큼 반도체 산업은 앞으로도 계속 성장 가능성이 크다”고 강조했다.

근무지

이천(1만2000여명 근무)과 청주(6000여명 근무)에 사업장이 있고, 분당에 R&D센터가 있다. 최종 근무지는 입사 후 결정

교대 근무

“양산/기술 직무는 교대 근무가능자에 한해 선발한다.”

호칭

“수평적 호칭을 사용한다. 기존의 수석, 책임, 선임, 사원 4개 직급 호칭을 TL로 명칭을 통일했다.”

TL : Technical Leader이라는 뜻입니다

직무소개

제조기술직

공정(제조)

공정(제조기술)은 연구소에서 개발 완료된 제품이 최고의 품질을 갖추어 생산될 수 있도록 다양한 생산 공정을 구현하는 업무입니다. Photolithography(포토 공정), Etch(식각 공정), Ion Implantation & Diffusion (이온 주입 및 확산 공정), Thin Film(박막 공정), CMP(연마 공정) 및 Cleaning (세정 공정) 등이 있습니다.

직무 양산/기술

공정(제조기술)은 연구소에서 개발 완료된 제품이 최고의 품질을 갖추어 생산될 수 있도록 다양한 생산 공정을 구현하는 업무.

1. Photolithography(포토공정), Etch(식각공정), Ion Implantaion & Diffusion(이온 주입 및 확산 공정), Thin Film(박막 공정), CMP(연마공정) 및 Cleaning(세정공정) 등의 역량 보유자

2. 선발 전공 : 전기전자, 반도체, 재료금속, 화학화공, 물리

Package

Silicon Device 집적도의 향상으로 더 이상 FAB 기술로는 구현이 불가능한 기술적인 한계가 다가옴에 따라, Electronic Packaging 기술을 통한 High Performance, Small Form Factor 구현이 절실히 요구되고 있습니다. 이에 따라 반도체의 전통적인 packaging 기술에서부터 CoC, POP, TSV 등 새로운 Packaging 기술 개발과 이들을 융합한 기술개발 및 제품 개발이 활발히 진행되고 있습니다. 이러한 Package 분야는 설계부문, 원부자재의 선정, 공정 설계, 신뢰성 확보/검증, 그리고 최적의 양산성과 품질을 달성할 수 있도록 하는 공정 최적화에 이르기까지 다양한 역할을 수행하면서 연관된 산업의 발전에 이바지 할 수 있습니다.

필요역량 – 향 후 한 차원 높은 차세대 Packaging 기술 개발을 위해서는 공정, 소재, 설비, 해석, 분석 분야 및 이를 Integration하는 기술도 중요하므로, 이공계의 전분야에 걸친 유능한 인재들이 필요합니다.

1) SK하이닉스 개요

1984년 한국 최초로 16Kb S램을 시험 생산한 이래 SK하이닉스는 더 작고 빠르면서도, 전력소모가 적은 혁신적인 반도체 제품들을 시장에 지속적으로 선보여 왔습니다. 생산제품은 DRAM, NAND Flash 및 MCP(Multi-chip Package)와 같은 메모리 반도체 제품이며, 2007년부터는 시스템 LSI 분야인 CIS(CMOS Image Sensor) 사업에 재진출하여 종합반도체 회사로 그 영역을 넓혀가고 있습니다.

2)SK하이닉스 개발 실적

구분

제품

효과

2018년 하반기

2세대 10나노급(1y) 8Gbit DDR4

“4 Phase Clocking” 설계 기술 적용 / Sense AMP 제어 기술 도입 / 19년 1분기 공급으로 수익성 개선에 기여

96단 512Gbit TLC

CTF와 PUC를 결합한 96단 4D NAND 개발 / 고용량 및 고성능 솔루션 라인업 강화로 시장 대응력 향상

2018년 상반기

72단 Enterprise SSD(SATA/PCIe)

72단 3D NAND 기반으로 자체 개발한 컨트롤러와 펌웨어를 탑재한 기업용 SSD 개발

2znm 8Gb HBM2 Gen2

HBM2 Gen1의 성능을 개선한 제품으로, 고객과의 협업체계 구축을 통해 향후 매출 확대 기여

1xnm 16Gb DDR4

1xnm Tech 기반의 고용량 DDR4 제품으로 고용량 / 고성능 컴퓨팅 제품 수요에 적기 대응하여 수익성 개선에 기여

2017년

3D 256Gb TLC

업계 최초로 개발한 72단 3D NAND FLASH로, 기존 48단 제품 동위 단위면적당 셀의 수가 많아 고용량 확보에 유리함, SSD와 모바일 기기에 적용 예정

2znm 8Gb GDDR6

2znm Tech. 기반의 GDDR6 제품으로 384개의 정보입출구를 활용해 초당 최대 768GB의 그래픽 데이터 처리가 가능. 향후 인공지능 및 가상 현실 등의 솔루션 등에 활용 예정

3D PCIe NVMe Client SSD

72단 3D NAND를 적용한 PCIe Client SSD 제품으로, 기존 36단 제품을 72단으로 전환하여 수익성 개선에 기여 예상

3D eMMC 5.1

기존 적용하던 36단 3D NAND를 72단으로 전환하고, 자체 개발한 eMMC 컨트롤러를 적용해 매출 확대에 기여 예상

2. SK하이닉스 공정

삼성전자의 Fab에서 이루어지는 8대 공정과는 다르게 SK하이닉스 Fab의 기본 공정은 크게 6개로 나뉘어져 있습니다.

6개의 기본 공정은 아래와 같습니다.

Photolithography, Etch, CVD/PVD, Diffusion, Cleaning, CMP

면접을 앞두고 있는 양산/기술 지원자라면 6개 공정의 실무자를 면접관으로 만나게 됩니다.

때문에 6개 공정에 대해 확실히 공부하고, 면접에 입장하는 것이 면접 필승의 지름길입니다.

각 공정에 대한 핵심 개념과 핵심 키워드에 대해 알아보도록 합시다.

1) Photo-lithography (노광기술)

- Wafer에 패턴을 만들기 위해, 패턴이 그려진 Mask를 이용하여 Photo Resist 도포 후 마스크를 정렬, 노광, 현상하는 공정입니다.

- 몇 천억 개의 트랜지스터를 한꺼번에 구성하기 위해 빛과 마스크를 사용하여 일괄적으로 회로를 형성하는 방식

- 광원의 종류에는 빛의 파장에 따라 KrF(불화크립톤), ArF(불화아르곤), Immersion ArF(액침 불화아르곤) 등이 있다.

* 감광액 (Photo Resist) : 회로를 형성하기 전에 웨이퍼에 얇게 코팅하는 액체 물질

- 감광액이 빛에 노출되면 변하는 화학적 성질을 이용하여 웨이퍼 위에 원하는 감광액 패턴만을 남길 수 있다.

- 감광액은 빛에 노출된 부분이 제거되느냐, 노출되지 않는 부분이 제거되느냐에 따라 양성(positive) PR과 음성(negative) PR로 분류된다.

* 액침 불화아르곤 (Immersion ArF) 노광기술 : 193nm 빛 파장을 갖는 불화아르곤 (ArF) 기술에 노광기와 웨이퍼 사이에 물을 넣어 빛 굴절률이 큰 액상 매체를 이용해 해상력을 높인 액침 기법을 더해 회로의 패턴을 미세하게 하는방식. 다만, 액침 불화 아르곤 노광기술로 형성할 수 있는 물리적 선폭 한계치는 38nm이다.

* 극자외선(Extreme Ultra Violet) 노광기술 : 액침 불화아르곤 방식보다 파장 길이가 1/14 미만으로 더욱 세밀한 회로 패터닝이 가능하며 현재 쓰이는 멀티 패터닝에 비해 제조시간을 단축시킬 수 있다. 다만, 기체를 포함한 모든 물질에 흡수되는 독특한 특성이 있어 진공 상태에서 노광이 이루어지고 빛을 투과하는 것이 아니라 여러 개의 박막 거울로 빛을 반사시켜야 하는 등 기술적 난이도가 높다.

* EUV

- EUV는 Extreme Ultra Violet을 말하며 극자외선 파장을 일컫습니다. 반도체 산업에서 EUV는 극자외선 파장의 광원을 사용하는 리소그래피 기술 또는 이를 활용한 제조공정을 말합니다.

EUV 공정은 기존 공정의 미세 패턴 한계를 극복할 수 있는 대안입니다. 기존에는 미세 패턴 공정을 위해 ArF 광원을 활용하여 DPT, QPT 등 수 차례 노광 공정을 반복했지만, EUV를 사용하면 공정 단계를 줄일 수 있어 생산성도 획기적으로 높일 수 있습니다.

* Photolithography 핵심 키워드

Mask

PR

빛(파장)

Soft bake

Alignment

Exposure

Align Key

HMDS

Polymer

Sensitizer

Spin coating

CAR

Reticle

DPT

QPT

Resolution

PEB(Post Exposure Bake)

Hard bake

OPC

DOF(Depth Of Focus)

PR strip

회절현상

Immersion

2) Etch

- 원하는 구조를 만들기 위해 Photo 현상 후 드러난 막질이나 실리콘을 화학적, 물리적으로 녹이거나 깎아 내는 공정입니다.

* Wet etch & Dry etch

Dry etch

Wet etch

특성

물리적, 화학적 반응

진공 Chamber

정확성이 좋아 패터닝을 작게 제작

고비용, 낮은 처리량(Low Throughput)

선택비(Selectivity)가 나쁘다

미세공정 적합

화학적 반응

대기, Bath

저비용, 쉬운과정

식각속도가 빠르다

선택비가 좋다

낮은 정확성, 웨이퍼 오염 위험

방향성

Anisotropic(비등방성)

Isotropic(등방성)

* Etch 핵심 키워드

Etch rate

Etch profile

Selectivity

Uniformity

Etchant concertration

Etchant pH

Etch time

Etch temperature

Isotropic

Anisotropic

Plasma

Wet etch

Dry etch

Ion bombardment

Aspect ratio

3) CVD/PVD

- Silicon 위에 박막을 형성하기 위해 원자 또는 분자 단위의 물질을 기체 상태로 분사하여 반응시켜 두께의 막질로 증착하는 공정 화학적 기상 증착(CVD)과 물리적 기상 증착(PVD)공정으로 나누어집니다.

* CVD & PVD & ALD

장점

단점

PVD

고품질 박막에 유리

불순물 오염 정도가 낮다(진공상태)

증발을 이용할 경우, 느린 증착속도

박막 접합성이 떨어진다.

CVD

좋은 접합성

저렴한 장비 비용

고온공정(재료적용 난제)

불순물 오염 정도가 높다

ALD

박막 도포성 우수

박막 두께조절이 쉽다

`박막성장 속도가 느리다

공정온도 제어가 어렵다

* CVD / PVD 핵심 키워드

Step coverage

Aspect ratio

Unifomity

APCVD

LPCVD

PECVD

HDPCVD

ALD

Thermal evaporation

E-beam evaporation

Sputtering

Plasma

Precursor

Adhesion

4) Diffusion

- 확산 원리를 이용하여 원하는 소자의 특성을 확보하기 위해, Silicon 표면에 주입된 불순물 이온들을 고온 가열을 통해 원하는 깊이만큼 고르게 분포시키는 공정입니다.

* Constant Source Diffusion

- 표면의 불순물의 농도를 일정하게 유지해서 진행하는 확산 공정입니다.

* Diffusion 핵심 키워드

Doping

Isotropic

Dopant

CSD (Constant Source Diffusion)

LSD (Limitied Source Diffusion)

RTA (Rapid Thermal Annealing)

Substitutional Impurity atoms

Interstitial impurity atoms

Pre-deposition step

Drive-in

Annealing

5) Cleaning

- Wafer 표면을 깨끗하게 만들기 위해, 필요 없는 막질이나 오염물질을 화학적, 물리적으로 제거하는 공정입니다.

* RCA cleaning

- 미국 RCA사에서 개발한 H2O2, NH4OH, HCl을 이용하여 유기물을 제거하는 방법입니다.

* Cleaning 핵심 키워드

Particle

Contamination

Micro-roughness

Wet cleaning

Dry cleaning

Acid cleaning

Alkaline cleaning

DI water

RCA

Spin

IPA

HF

NH4OH

H2O2

HCl

SC1

SC2

6) CMP

- 단차에 의한 후속 공정 불량을 막기 위해, 울퉁불퉁한 막질이나 물질을 화학적 반응과 기계적 힘을 이용하여 연마하는 공정입니다.

* DOF (Depth Of Focus)

- 반사 또는 굴절을 통해 특정 위치에 선명한 상이 맺힐 때, 피사체와 상 사이의 거리입니다.

* CMP 핵심 키워드

Damascene

Dishing

Erosion

Selectivity

DOF (Depth of Focus)

Cu

Full CMP

Kp

Slurry

Conditioner

Pad

Platen

Planarization

RR (Removal rate)

Press

Velocity

* Clening 공정과 CMP 공정을 합쳐서 C&C 공정이라고 불리기도 합니다.

- 웨이퍼(wafer)

아무 것도 없는 순수한 실리콘 웨이퍼, 반도체 제조를 위한 베이스가 되는 재료

- CMP(Chemical Mechanical Polishing) 공정

화합물을 사용하여 웨이퍼를 기판으로 사용하기 전에 그 표면을 평탄화 하는 공정

- 산화(Oxidation) 공정

웨어퍼 표면을 보호하는 산화막을 만드는 공정

- 포토(Photo) 공정

필름 역할을 하는 마스크(Mask)를 인화지 역할을 하는 웨이퍼 위에 패턴을 입히는 공정

- 식각(Etch) 공정

필요한 회로 패턴을 제외한 나머지 부분을 제거하는 공정

- 박막 증착(Thin Film, Deposition) 공정

웨이퍼가 반도체의 성질을 가질 수 있도록 표면에 불순물 확산, 박막 형성 하는 공정

- 금속 배선(Metallization) 공정

외부에서 얻어지는 전기적 에너지를 받아 소자들끼리 신호가 섞이지 않고 전달되도록 선을 연결하는 공정

-불량테스트 EDS(Electrical Die Sorting) 공정

웨이퍼 상태에서 이뤄지는 TEST로 불량을 선별하는 공정

- 패키징(Packaging) 공정

외부 전원 공급 및 입출력 신호 전류들과 연결, 칩을 외부 환경으로부터 보호하는 공정

출처: https://www.skcareersjournal.com/716?category=696984 [SK채용 공식 블로그]

(1) 웨이퍼 공정

1. 웨이퍼를 만드는 데 필요한 재료 : 실리콘 – 초크랄스키법 (녹는점내림)

웨이퍼를 만들기 위해서는 실리콘이 필요합니다. 실로콘은 지구상에 아주 풍부할 뿐만 아니라, 독성이 없어서 환경적으로 우수하다는 장점을 가지고 있죠. 혹시 반도체 집적회로(Semiconductor Intergrated Circuit)에 대해 들어 보셨나요? 반도체 집적회로는 많은 소자를 하나의 칩 안에 집적한 전자부품을 말하는데요. 다양한 기능을 처리하고 저장하기 위해 만들어졌죠. 그리고 ‘웨이퍼(Wafer)’란 그 집적회로를 올리기 위한 기반을 말합니다. 웨이퍼는 대부분 모래에서 추출한 규소, 바로 실리콘(Si)을 성장시켜 만든 단결정 기둥을 적당한 두께로 얇게 썬 원판물입니다.

2. 웨이퍼 제조 공정

1) 잉곳(Ingot) 만들기 : 실리콘은 모래에서 추출합니다. 이를 반도체 재료로 사용하기 위해서는 정제 과정을 거칩니다. 순도를 높이는 과정이죠. 고순도로 정제된 실리콘(Si) 용액을 주물에 넣어 회전시키면 실리콘 기둥이 만들어지는데요. 이를 잉곳(ingot)이라고 부릅니다. 이 잉곳은 실리콘 결정 성장기술인 초크랄스키(Czochralski)법 또는 플로팅존(Floating Zone)법 등을 이용하여 얻을 수 있습니다. 수 나노미터(nm)의 미세한 공정을 다루는 반도체용 잉곳은 실리콘 잉곳 중에서도 초고순도의 잉곳을 사용합니다.

2) 잉곳 절단하기(Wafer Slicing) : 잉곳의 말단을 제거하고, 다이아몬드 톱을 이용하여 균일한 두께의 얇은 웨이퍼(Wafer)로 절단합니다. 잉곳의 지름이 웨이퍼의 크기를 결정하죠. 이때, 사용할 수 있을 정도에서 얇게 절단할수록 제조비용이 절감이 돼서 최근엔 점점 얇게 절단하고 있다고 합니다. 지름의 크키 또한 커지는 게 대세인데요. 이 역시 넓을수록 많은 양의 반도체 칩을 제조할 수 있기 때문이랍니다.

3) 웨이퍼 표면 연마하기(Lapping, Polishing) : 1), 2) 과정을 통해 만들어진 웨이퍼는 표면이 아주 거칠고 울퉁불퉁한 흠결이 많기 때문에 실제 반도체 공정에 이용하기 힘듭니다. 따라서 표면을 연마하여 매끄럽게 만들어주어야 하는데요. 연마액과 연마 장비를 통해 웨이퍼 표면을 매끄럽게 갈아냅니다.

3. 반도체 웨이퍼 명칭

: 아직 가공되기 전의 웨이퍼에 여러 단계의 물리적, 화학적 가공을 거쳐 표면에 IC를 형성시키게 됩니다. 이렇게 IC칩까지 완성된 웨이퍼의 각각의 명칭을 설명해드리겠습니다.

1) 웨이퍼(Wafer) : 반도체 집적회로를 만드는 데 사용하는 주요 재료로, 주로 실리콘, 갈륨, 아세나이드 등을 성장시켜 얻은 단결정 기둥을 적당한 지름으로 얇게 썬 얇은 원판 모양의 판을 말합니다.

2) 스크라이브 라인(Scribe Line) : 칩 사이의 경계로, 아무 전자회로가 없는 부분이며, 웨이퍼를 개개의 칩으로 나누기 위한 분리 선을 말합니다. 다이아몬드 톱으로 잘라낼 수 있는 폭을 말하는 것이지요.

3) 플랫존(Flat Zone) : 둥근 웨이퍼의 구조를 판별하기 위해 만든 평평한 부분을 말하며, 플랫존은 웨이퍼 가공 시에 기준 선이 됩니다. 이 플랫존을 기준으로 웨이퍼의 수직, 수평을 판단하게 되는 것이죠.

4) 다이(Die) : 둥근 웨이퍼 위에 작은 사각형들이 밀집되어 있는데, 이 사각형 하나하나가 전자 회로가 집적되어있는 IC칩을 말합니다.

(2) 산화(Oxidation) 공정

1. 산화 공정이란?

가장 먼저 산화 공정이 어떤 말인지 알고 가야겠죠? ‘산화 공정’이란, 실리콘(Si) 기판 위에 산화제(물(H2O), 산소(O2))와 열에너지를 공급하여 이산화규소(SiO2) 막을 형성하는 공정을 말합니다.

이때 만들어지는 산화막은 회로와 회로 사이에 누설 전류가 흐르는 것을 막아줄 뿐만 아니라, 이온주입공정에서 확산 막아주는 역할, 식각 공정에서 엉뚱한 곳이 잘못 식각 되는 것을 막는 식각 방지막 역할을 합니다. 이렇게 다양한 종류의 보호막이 되어 웨이퍼를 지켜주는 것이죠. ‘산화’의 이해가 어려우시다면, 철(Fe)이 녹스는 현상을 생각하시면 됩니다.

2. 산화 공정 방법 : 산화 공정 방법에는 열을 통한 열산화(Thermal Oxidation), 화학적기상증착산화(Chemical Vapor Deposition), 전기화학적산화(Electrochemical Oxidation) 등의 종류가 있습니다. 그 중 가장 많이 사용되는 방법은 고온에서 얇고 균일한 실리콘 산화막을 형성하는 열산화 방법입니다. 이러한 열산화 방법은 산화반응에 사용되는 기체에 따라 크게 습식 산화와 건식 산화로 분류할 수 있습니다.

1) 건식 산화(Dry Oxidation) : 건식산화는 순수한 산소(O2)만을 이용하기 때문에 산화막 성장속도가 느려 주로 얇은 막을 형성할 때 쓰입니다. 성장속도가 느릴 때 얇은 막을 형성하기 유리한 까닭은, 성장속도가 느릴수록 막의 두께를 조정(Control)하기 쉽기 때문입니다. 쉽게 생각하면, 내가 세숫대야에 물을 아주 조금만 채우고 싶을 때, 수도꼭지를 한번에 많이 열어 콸콸 붓기보다, 아주 조금만 열어 조금씩 떨어지게 하는 상황을 생각하면 쉽게 이해가 될 것입니다. 이렇게 얇은 막을 형성할 수 있는 건식 산화는 전기적 특성이 좋은 산화물을 만들 수 있습니다.

2) 습식 산화(Wet Oxidation) : 습식산화는 산소(O2)와 함께 수증기(H2O)를 사용하기 때문에 산화막 성장속도가 빠르고 두꺼운 막을 형성할 수 있지만, 건식 산화에 비해 산화층의 밀도가 낮습니다. 따라서 산화막의 질이 건식산화에 비해 비교적 안 좋다는 단점이 있습니다. 동일한 온도와 시간에서 습식산화를 통해 얻어진 산화막은 건식산화를 사용한 것보다 약 5~10배 정도 더 두꺼운 경향을 보입니다.

3. 이 외에 산화막 성장 속도에 영향을 미치는 것들 : 반도체 사이즈는 점점 작아지고, 이 와중에 산화막은 보호막의 역할을 위해 꼭 필요하므로 산화막의 두께는 반도체 사이즈를 결정하는 데에 아주 중요한 요소로 작용합니다. 따라서 산화막의 두께를 줄이기 위해 산화 공정의 다양한 변수를 조율하게 됩니다. 2번 항목에서 설명 드렸던 습식 산화, 건식 산화도 그 변수의 한 종류라고 말할 수 있으며, 그 이외에도 웨이퍼의 결정 구조, 더미 웨이퍼(가스를 정면으로 닿거나 나중에 닿는 부분의 산화 정도 차이를 줄이기 위해 희생 웨이퍼인 더미 웨이퍼를 활용하여 가스의 균일도를 맞추어 줄 수 있음), 도핑 농도, 표면 결함, 압력, 온도, 시간 등이 산화막의 두께에 영향을 줄 수 있습니다.

(3) 포토(Photo Lithography) 공정

1. 포토 공정 : 제가 서론에서 포토공정을 반도체 설계 회로를 “찍어내는”이라고 표현한 것 모두 기억하시나요? ‘찍다’하면 기억나는 게 무엇인가요? 바로 카메라입니다. 포토공정은 필름카메라로 사진을 찍어 현상하는 것과 같은 원리로 진행됩니다. 조금 구체적으로 이야기하면 반도체 표면 위에 사진 인쇄 기술을 이용하여 회로 패턴을 만들어 넣는 기술을 말합니다. 빛에 반응하는, 필름 카메라에서 바로 필름에 해당하는 감광성 고분자 물질(PR, Photoresist)를 얇게 바른 후 마스크를 올려놓고 그 위에 빛을 가하여 원하는 패턴을 형성하는 과정을 말합니다.

2. 감광성 고분자 물질(PR, Photo Resist)

: PR은 3가지 물질로 이루어져 있습니다. PR을 보관하기 위해 외부 빛의 노출을 방지하고자 사용하는 액체인 Solvent, 폴리머 결합으로 이루어진 물질인 Resin, 그리고 마지막으로 빛에 반응하는 화합물 Photoactive Compound(PAC), 이 PAC는 크게 Positive PR과 Negative PR로 나누어집니다.

3. 포토공정 과정

포토공정 과정은 Surface Preparation -> Spin Coating -> Soft Baking -> Alignment & Exposure -> Post-expose Baking -> Develop -> Rinse-dry -> Hard Baking으로 이루어져있습니다. 이렇게 보니 무슨 말인지 도통 모르겠죠? 그래서 쉽게 설명하기 위해 이 전체 공정을 위에서 설명한 PR과정, 노광, 웨이퍼에 회로도를 찍어내는 Develop 과정. 이렇게 크게 세 개의 과정으로 구분할 수 있습니다.

1) 노광

: 노광 과정에는 Mask Layer 사이를 정확한 위치에 맞추는 Alignment과정과 감광막에 빛을 쏘아 패턴이 형성되도록 하기 위한 과정인 Exposure로 나눌 수 있습니다. 이 과정을 거치면 패턴이 형성됩니다. 노광은 필요에 따라 세 가지 모드로 진행될 수 있습니다.

2) Develop

: 현상(Develop)은 필름 카메라에서 사진을 현상하는 과정과 같으며, 이 공정에서 패턴의 모양이 결정됩니다. 현상 과정을 지나면, 노광에 의해 빛에 노출된 부분, 노출되지 않은 부분을 선택적으로(Positive, Negative PR) 제거하여 회로 패턴을 형성하게 됩니다.

출처: https://www.skcareersjournal.com/908?category=696984 [SK채용 공식 블로그]

(4) 에칭(Etching) 공정

1. 식각(Etching)공정이란?

이전 3번째 포토(Photo Lithography) 공정에서 ”밑그림을 그린다~”라는 표현 기억하시나요? 이번 식각(Etching)공정에서는 밑그림 중 불필요한 부분을 없애는 즉, 회로의 패턴 중 필요한 부분만 남기고 불필요한 부분은 깎아내는 작업을 수행합니다. 더 자세히 말하자면 포토(Photo Lithography)공정에서 부식방지막(Photo Resist)을 형성했다면 식각 공정에서는 액체 또는 기체의 etchant를 사용하여 부식을 진행하여 불필요한 부분을 없애는 작업입니다. (이때 etchant 란 부식을 진행하는 물질을 통칭하는 말입니다.) 이러한 에칭 기법은 동판화를 작업하는 미술에서 자주 쓰이는 방법인데요 19세기 화가인 피사로(Camille Pissaro)와 드가(Edgar Degas) 역시 에칭을 이용해서 정교하고 세밀한 선을 살린 작품을 많이 만들어 냈다고 합니다.

2. 건식(Dry) 식각방법과 플라즈마(Plasma) : 에칭 기법의 동판화 미술과 반도체 공정은 방법의 차이가 존재합니다. 미술에선 날카로운 조각도구들을 이용해 회로를 만들어 냈다면 공정에선 감광액 (Photo Resist)으로 보호막을 먼저 만들어 냅니다. 그리고 나서 식각(부식)을 진행하게 되는 것이죠.

Wet Etching

Dry Etching

액상의 화학용품 사용

기체 가스 사용

상대적으로 가격이 저렴

상대적으로 가격이 높고 방법이 까다로움

상대적으로 균일도 높음

극미세 회로 식각 가능

이러한 식각 공정은 크게 반응을 일으키는 물질의 상태에 따라 습식과 건식 두 가지로 나눌 수 있는데요. 건식은 습식에 비해 많은 비용이 들고 방법이 까다롭다는 단점이 있지만 최근 수율의 증대와 극미세 회로 식각을 위하여 건식이 널리 사용되고 있다고 합니다!

그렇다면 건식 식각에 대해 더 자세히 알아보도록 할까요? 건식 식각은 흔히 플라즈마(Plasma) 식각이라고도 합니다. 플라즈마? 어디서 많이 들어본 용어 같지만 다소 생소하게 들립니다. 플라즈마란 고체, 액체, 기체 상태를 넘어선 물질의 제 4상태를 말합니다.

진공 챔버(Chamber)에 Gas를 주입한 후 전기에너지를 공급하여 이 “플라즈마” 라는 상태를 만들어내게 됩니다. 플라즈마 상태에서는 많은 수의 자유전자, 이온, 중성원자 또는 이온화된 기체 분자가 존재하게 되는데요 이 때 중요한 건 이온화의 연쇄반응(Avalanche) 입니다.

먼저 챔버(Chamber)에 전기에너지를 공급하면 자기장이 생기게 되고 이러한 자기장은 자유전자에 영향을 주게 됩니다. 높은 에너지를 가진 자유전자들은 주변의 중성 원자나 분자와 충돌하게 되고 다시 여기서 나온 자유전자가 다른 중성의 원자나 분자와 충돌하게 됨으로써 연쇄적인 이온화 반응이 일어나 “플라즈마 상태” 를 만들어 내는 것이지요.

플라즈마 상태에서 떨어져 나온 반응성 원자 (Radical Atom)가 웨이퍼 표면의 원자들과 만나 강한 휘발성을 띠면서 표면에서 분리되게 됩니다. 이 과정에서 감광액 (Photo Resist)으로 보호되지 않은 막은 제거되는 것이지요. 바로 이러한 방법이 건식 식각이라 할 수 있겠습니다.

3. 식각(Etching)이 잘되어야 하는 이유?!

그렇다면 식각을 잘해야 하는 이유는 무엇일까요? 그 것은 바로 식각은 곧 수율과 이어지기 때문입니다. 잘못된 식각으로 인하여 회로 부분이 끊기거나 균일하지 않으면 결과적으로 생산된 반도체 칩에 오류가 생기고 원하는 동작을 수행할 수 없게 되는 현상을 초래하기 때문이죠. 따라서 식각을 진행할 때는 여러 주요인자들이 존재합니다.

#1 균일도 (Uniformity)

균일도(Uniformity)란 식각이 얼마나 고르게 진행됐는지를 의미합니다. 균일도가 중요한 이유는 회로의 각 부분마다 식각된 정도가 다르다면 특정 부위에서 칩이 동작하지 않을 수 있기 때문이죠. 반도체 회로의 모든 부분에서 식각이 같은 속도로 같은 양만큼 진행된다면 정말 깔끔한 반도체를 얻을 수 있을 텐데요. 아쉽게도 오차는 존재하기 마련이기 때문에 이러한 균일도를 최대한 높이려고 많은 기업들이 앞다투어 노력하고있죠.

#2 식각 속도(Etch Rate)

식각 속도는 일정시간동안 막이 얼마나 제거 됐는지를 의미합니다. 플라즈마 상태의 원자와 이온의 양 또는 그 원자나 이온이 가지고 있는 에너지에 따라 식각의 빠르기가 결정됩니다. 당연히 양이 많고 에너지가 높으면 식각 속도는 증가하게 됩니다. 따라서 이러한 양과 에너지를 조절하여 식각의 알맞은 속도를 맞출 수 있는 것이지요. 이 외에도 막질에 따라 서로 다른 식각량을 비율로 나타낸 선택비(Selectivity) 등의 고려 사항들이 존재하며 이러한 모든 세부 사항들을 좀 더 정교하게 진행하려는 많은 노력들이 식각(Etching) 공정 팀에서 이루어지고 있죠.

(5) 확산(Diffusion) 공정

1. 확산(Diffusion) 공정이란?

먼저 확산(Diffusion) 공정이란 웨이퍼에 특정 불순물을 주입하여 반도체 소자 형성을 위한 특정 영역을 만드는 것입니다. 식각 과정을 거친 회로 패턴의 특정 부분에 이온 형태의 불순물을 주입하여 전자 소자의 영역을 만들어 주고, Gas간 화학 반응을 통해 형성된 물질을 웨이퍼 표면에 증착함으로써 여러가지 막을 형성하는 공정을 말합니다.

2. 들어가기 전에

확산 공정을 들어가기 전에 오늘 날에는 확산을 통한 공정을 진행하기보단 이온 주입(Ion Implantation) 또는 rapid thermal annealing 과정을 통해 진행한다는 점을 참고 하시는 게 좋습니다! 하지만 그러한 실제 공정 단계를 알기 위해 먼저 확산 공정에서의 다양한 문제점을 이해하고 가는 것이 중요합니다. 공정에서 말하는 확산 공정은 이온 주입과 annealing 과정을 포함한다고 봐도 무방할 것 같습니다.

*annealing 이란? 금속 재료를 적당한 온도로 가열한 다음 서서히 냉각시키는 조작을 일컬음

3. 확산 공정의 기본

<침입형과 치환형 입자>

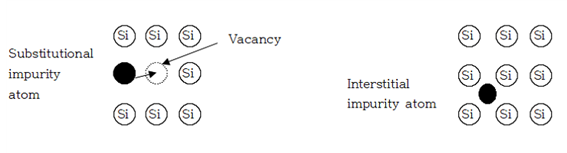

확산 공정은 먼저 실리콘 막에 얇은 불순물을 도핑 하는 것으로부터 시작합니다. 이때 도핑되는 방법에 따라 치환형 (Substitutional impurity atoms) 또는 침입형 (Interstitial impurity atoms) 두 가지 유형으로 나뉘는데요, 위 그림과 같이 말 그대로 실리콘 결정에 불순물이 “치환”해서 들어가느냐 또는 “침입”해서 들어가느냐 에 따라 나뉘는 것입니다.

모든 물질에는 그 물질의 고유한 패턴인 ‘격자’라는 것이 존재합니다. 즉 Si 격자 라고 하면 실리콘 입자들이 어떤 모습으로 분포해 있는지를 나타내는 말이지요. 격자라는 것이 이론적으로는 일정한 간격으로 표현되지만 실제 Si 격자는 몇몇 입자의 displacing (있어야 할 자리에 있지 않은 현상) 때문에 Vacancy 가 생길 수 밖에 없습니다. 이러한 Vacancy 에 치환형 입자가 들어가게 된다면 실리콘과는 조금 다른 물리적 전기적 특성을 띠게 되겠죠? 침입형 입자 또한 마찬가지 입니다. 이러한 침입형 또는 치환형 입자에는 붕소(Boron), 인(Phosphorus), 비소(Arsenic), 안티몬(Antimony) 등 이 있습니다.

4. 확산 공정에서 중요한 두 가지 조건

지난 시간 에칭 공정에서 주요 인자였던 균일도와 식각 속도 기억하시나요? 모든 반도체 제조 공정이 그러하듯 확산 공정도 그 과정이 균일하게 이루어져야 합니다. 따라서 실리콘에 불순물을 주입하여 원하는 IC(집적회로)를 모델링하기 위해, 중요한 두 가지 요소가 있습니다.

1) Constant Source Diffusion

줄여서 CSD라고 표기하기도 하는데요 이는 확산 공정이 진행되는 동안 실리콘 표면의 불순물의 농도가 일정해야 함을 말합니다. 이 때 단위 면적당 총 불순물 입자의 수 즉 농도를 나타내는 말로 “dose”량 이라는 표현을 사용합니다.

2) Limited Source Diffusion

LSD. 이는 공정이 진행되는 동안 dose량이 일정해야 함을 말합니다. 또한 만약 실리콘 격자에 너무 많은 양의 불순물을 doping하게 되면 실리콘을 사용하는 의미가 없어지게 되겠죠?

5. 확산의 두 가지 STEP

확산은 두 가지 step으로 진행됩니다. 앞서 말한 CSD는 주로 실리콘의 얇은 표면 막에 불순물이 들어갈 때부터 적용됩니다. 이를 가리켜 pre-deposition step 이라고 말하지요. 두 번째 step은 (LSD) drive-in입니다. 이는 실리콘 표면으로부터 얼마나 깊게 까지 dose를 할 것이냐를 말하는 것이지요.

(6) 박막증착 공정

1. 박막 입히기 정말 막막...

위에서 언급한 것처럼 박막이란 정말 얇은 막을 말합니다. 웨이퍼보다도 훨씬 얇은 막을 어떻게 입히지, 라는 생각에 증착 공정이란 정말 막막해 보입니다. 반경이 100mm인 웨이퍼에 1 μm 박막을 씌우는 것은 마치 반경이 100m인 땅에 테이프 두께보다 더 얇은 막을 정교하게 입혀야 하는 것이니 정말 막막하지 않으신가요? 따라서 이러한 박막 공정은 정말 정확하고 세밀한 작업을 요합니다. 모든 반도체 공정이 그렇듯 말입니다.

2. PVD와 CVD

우선 박막을 만드는 방법은 크게 두 부류로 나뉩니다. PVD(Physical Vapor Deposition)와 CVD(Chemical Vapor Deposition)이죠. 두 방법의 차이는 ‘물리적인 방법으로 증착하느냐, 화학적으로 증착하느냐’ 입니다. PVD는 또 크게 Thermal evaporation , E-beam evaporation , Sputtering으로 나뉩니다. 이렇게 말하니 벌써부터 막막하신가요? 따라서 아래 표를 준비했습니다!

<Deposition 의 종류를 나타낸 표 > 표를 보니 박막을 입히는 방법이 정말 많다는 것을 알 수 있겠죠? 이렇게 방법이 많은 이유는 각 방법마다 사용하는 재료가 다르고 장단점이 다 다르기 때문입니다.

먼저 PVD는 금속박막 증착에 주로 사용되고 화학반응을 수반하지 않는다는 게 특징입니다. 즉 물리적인 방법으로 박막을 증착한다는 것인데요. 그 중 하나인 Sputtering을 살펴보도록 하죠.

Sputtering 이란 아르곤(Ar) 가스를 이용해 증착하는 방식입니다. 먼저 진공 챔버에 Ar가스와 자유전자가 존재합니다. 이때 Ar 가스에 높은 전압을 가해주게 되면 Ar -> Ar+ 이온으로 변화하게 됩니다. 증착이 되야 할 기판엔 (+)전압을, 증착하고자 하는 물질인 타겟 층엔 (–)전압을 걸어줍니다.

자유전자와 Ar 기체 간의 충돌로 이온화된 Ar+는 (-) 상태인 Target층과 부딪힙니다. 이후 Target 물질이 분리되어 기판(Substrate) 쪽으로 증착이 됩니다. 이후 Ar과 자유전자의 충돌은 끊임없이 일어나며 증착이 진행됩니다.

<Sputtering 모식도 > 두 번째 방식으로는 CVD가 있습니다. CVD란 Chemical Vapor Deposition 의 줄임말로 우리말로는 화학기상증착법이라고 불립니다. 가스의 화학 반응으로 형성된 입자들을 외부 에너지가 부여된 수증기 형태로 쏘아 증착시키는 방법인데요. 이는 도체, 부도체, 반도체의 박막 증착에 모두 사용 가능하다는 장점이 있습니다. 이러한 이유로 대부분의 반도체 공정에서는 화학적 기상증착방법을 사용하고 있습니다. 이중 특히 PECVD (Plasma Enhanced CVD)는 플라즈마를 사용해 저온 공정이 가능하고 두께 균일도를 조절할 수 있으며 대량 처리가 가능하다는 장점 때문에 가장 많이 이용되고 있습니다.

<PECVD (Plasma Enhanced Chemical Vapor Deposition) 모식도> 여러분 혹시 식각(Etching)과정에서 “플라즈마” 상태 기억나시나요? 플라즈마란 이온, 자유전자, 중성원자 들로 이루어진 물질의 제4상태를 말합니다. PECVD의 원리를 간단히 설명하자면 반응시킬 기체를 주입하고 플라즈마 상태를 만들기 위해 전압을 수직으로 걸어줍니다. 따라서 플라즈마 상태로 이온화된 기체들이 서로 화학반응을 하여 원하는 물질이 기판에 고르게 쌓이게 되고 나머지 이온들은 결합하여 기체로 배출되게 되는 것이죠. 이해가 되셨나요?

3. PVD와 CVD 장단점과 주요인자

장점

단점

PVD

- 저온공정

- 진공상태 (불순물 오염 적음)

- 증착속도 느림

- 박막 접합성 떨어짐

CVD

-접합성 및 박막 품질 좋음

- 고온 공정으로 인한 재료 선택 문제

- 두께 조절 컨트롤 어려움 존재

<PVD, CVD 장단점을 나타낸 표>

PVD와 CVD는 방법이 다를 뿐만 아니라 장단점도 다르며 그 안에서의 방법들도 많은 차이가 있습니다. 증착에서의 주요 인자로는 품질, 두께 균일도, Step Coverage, Filling이 있는데요, 모두 균일함을 나타내는 요소라고 할 수 있겠습니다.

(7) 금속(Metalization)공정

#금속 공정이란?

금속 공정(Metalization)은 금속 형성 공정 혹은 금속 배선 공정이라고도 불립니다. 반도체는 각 층의 연결을 통해 회로의 작동이 이루어지는데요. 이를 위해 필요한 공정이 ‘금속 공정’입니다. 외부에서 얻어지는 전기적 에너지를 받아 소자들끼리 신호가 섞이지 않고 전달되도록 선을 연결해주어야 합니다.

#금속 공정에 사용되기 위한 ‘금속의 조건’

모든 종류의 금속이 금속 공정에 사용될 수 있을까요? That’s No No. 전극층을 형성하고 각 층을 연결하기 위해 사용되는 금속에는 몇 가지 조건이 있습니다.

1) 웨이퍼와의 부착성 : 반도체 기판, 즉 실리콘 웨이퍼와의 부착성이 좋아야 합니다. 즉, 쉽게 부착되고 부착 강도가 뛰어나 얇은 박막으로 증착 할 수 있어야합니다.

2) 낮은 전기저항 : 금속선은 회로패턴을 따라 전류를 전달하는 역할을 합니다. 그러므로 전기저항이 낮은 물질이어야 합니다.

3) 열적•화학적 안정성 : 금속 배선 공정 이후의 공정에서 만들어 놓은 금속선의 특성이 변하지 않는 것이 중요합니다. 따라서 이후 공정에 대해 열적, 화학적 안정성이 뛰어난지 꼭 고려해주어야 합니다.

4) 패턴 형성의 용이성 : 반도체 회로 패턴에 따라 금속선을 만드는 작업 과정이 쉬운지를 확인해야 합니다. 좋은 금속 재료이더라도 식각 등 공정 특성에 맞지 않으면 배선 재료로 쓰이기 어렵기 때문입니다.

5) 높은 신뢰성 : 신뢰성이란 반도체의 향후 품질을 말합니다. 즉 금속을 선택할 때 반도체의 좋은 품질을 오랜 기간 유지할 수 있는지를 고려해주어야 합니다. 집적회로 기술의 발전으로 점점 그 크기가 미세해지고 있는데요. 금속 배선 또한 작은 크기의 단면에서 끊어지지 않고 오래갈 수 있는지 따져야 합니다.

6) 제조 가격 : 위 다섯 개의 조건을 만족시키더라도 너무 비싼 재료라면 대량 생산을 하는데 어려움이 있기 때문에 부적합합니다.

이러한 조건을 만족시키는 단일층 재료로는 알루미늄(Al), 구리(Cu) 등이 있고, 다층구조로는 티타늄(Ti) 텅스텐(W)등이 있습니다.

# 금속 박막 형성 과정

조건에 맞는 금속이 준비되었으면 이제 본격적으로 금속 공정을 시작해야겠죠? 단일층 재료로 많이 사용되는 알루미늄(Al)과 구리(Cu)의 공정을 조금 더 자세히 알아봅시다.

<Al 증착 ▶ PR Coating ▶ Photo ▶ Develop ▶ Al Etch ▶ PR Strip> 알루미늄은 저항이 낮고, 산화막(SiO2)과의 접착성이 우수해 금속 공정에 적합한 물질입니다. 하지만 실리콘과 만나면 섞이려는 성질이 있어서, 접합면 사이에 Barrier metal이라 불리는 금속을 넣어 상하는 것을 방지해주어야 합니다. 금속 배선 공정 역시 증착을 통해 이루어지는데, 알루미늄의 경우 주로 Sputtering에 의해 증착됩니다.

장점

단점

- 가격이 저렴하다

- 박막 상태에서도 bulk 상태와 비슷한 높은 전기전도도를 가짐

- 박막 증착이 쉬움

- 산화막(SiO2)과의 접착력이 우수하다

- Hillock이 발생

- 전자이동으로 수명이 짧다

- 부식이 잘됨

<SiO2 증착 ▶ PR Coating ▶ Photo ▶ Develop ▶ SiO2 Etch ▶ PR Strip▶ Cu 매립 ▶ CMP>

장점

단점

- 알루미늄보다 비저항이 낮다

- 알루미늄보다 녹는점이 높고 diffusivity가 낮다

- electromigration이 억제되서 반도체의 신뢰도가 높다

- etch이 어려움

- SiO2를 확산으로 지나가서 확산 방지막이 필요함

- 패턴형성이 어려워 damascene 공정을 사용해야함

#금속 박막 형성 방법

금속 박막을 형성하는 방법에는 크게 세 가지가 있습니다. 화학적 반응으로 박막을 형성하는 방법인 CVD(Chemical Vapor Deposition), 물리적 기상 증착법인 PVD(Physics Vapor Deposition)가 있습니다. 또, PVD와 CVD 방식의 한계를 극복하기 위해 원자층을 증착하여 박막을 형성하는 ALD(Atomic Layer Deposition)이 주목을 받고 있습니다.

[ PVD ]

장점

단점

- 저온 증착이 가능

- 모든 물질을 증착할 수 있음

- 불순물이 적음

- Step coverage가 좋지 않음

- 조성 조절이 어려움

- 얇은 두께를 조절하기 어려움

[ CVD ]

장점

단점

- Step coverage가 좋음

- 조성이나 두께를 조절하기 유리함

- 대부분의 공정이 고온에서 진행됨

- 반응 변수가 복잡함

- 유독 가스를 사용하므로 위험함

[ ALD ]

장점

단점

- CVD 대비, 낮은 온도에서 공정할 수 있음

- Step coverage가 좋음

- CVD 대비 조성이나 두께 조절이 유리함

- 유독 가스를 사용하므로 위험함

(8) Wafer test & Packaging 공정

선물을 주기 전에 정성스레 쓴 편지에 오탈자는 없는지, 빠진 선물은 없는지, 케이크의 상태는 양호한지 최종적으로 체크하는 단계 ☞ 반도체 공정에서는 “Wafer TEST공정”

# Wafer TEST공정이란?

Wafer TEST공정은 웨이퍼 상태에서 여러가지의 검사를 통해 각 칩들의 상태를 확인하는 과정을 말합니다. 지난 컨텐츠에서 살펴 본 공정과 최종적인 제품의 형태를 갖추는 패키징 공정 사이에 진행되는데요. 이 과정을 통해 웨이퍼 상태의 반도체 칩의 불량여부를 선별할 수 있고, 설계 상의 문제점이나 제조 상의 문제점을 발견해 수정할 수 있습니다. Wafer TEST공정을 거치면 이후 진행되는 패키징 공정 작업의 효율이 높아집니다.

# Wafer TEST공정의 네 단계

Wafer TEST공정은 반도체의 수율을 높이기 위해 반드시 필요한 공정입니다. 수율은 쉽게 말해 웨이퍼 한 장에서 사용할 수 있는 정상적인 칩 수를 계산한 것인데요. 수율이 높을수록 생산성이 높다는 의미가 됩니다. 그러므로 높은 수율을 얻는 것은 매우 중요합니다. 그렇다면 Wafer TEST공정은 크게 어떻게 이루어져 있을까요?

1) EPM & WFBI

EPM은 Electrical Parameter Monitoring의 약자로 반도체 직접회로(IC) 동작에 필요한 개별소자들의 전기적 직류 전압, 전류 특성의 파라미터를 테스트해 잘 작동하는지를 판별하는 과정입니다. WFBI는 Wafer Burn In의 약자로 웨이퍼에 일정 온도의 열을 가한 다음 AC/DC 전압을 가해 잠재적 불량 요인을 찾아내는 과정입니다. 이 두 과정을 통해 제품 초기에 발생하는 높은 불량률을 효과적으로 제거할 수 있습니다.

2) Hot & Cold Test

전기적 신호를 통해 웨이퍼 상의 각 칩들에 이상이 있는지 판정합니다. 이상이 있는 칩 중 수선이 가능한 것들은 수선 공정에서 처리할 수 있도록 정보를 저장하는데요. 이 때, 특정 온도에서 발생하는 불량을 판별하기 위해 높은 온도 혹은 낮은 온도에서 테스트합니다.

3) Repair & Final Test

불량품에 대해서는 Electrical Rupture를 통해 Repair하고, 수선이 끝나면 Final Test를 통해 수선이 제대로 이루어졌는지 검증하고 양품인지 불량품인지를 최종적으로 판단합니다.

4) Inking

말 그대로 ‘잉크를 찍는 공정’입니다. 불량 칩에 특수 잉크를 찍어 육안으로 불량칩을 식별할 수 있도록 하는 과정인데, 과거에는 실제 잉크를 찍었지만 현재는 실제 잉크를 찍지 않고 전산화하여 관리하고 있습니다. 불량으로 전산 처리된 칩은 조립 작업이 진행되지 않으므로 시간이나 경제적 측면에서 긍정적인 효과가 있겠죠? Inking공정까지 마친 웨이퍼는 품질 검사를 거쳐 조립 공정으로 이동됩니다.

# Packaging공정이란?

Packaging공정을 더 세부적으로 나누면, Package공정과 Package Test공정으로 나눌 수 있습니다.반도체 칩은 전자기기의 구성품으로서 필요한 위치에 장착되어야 하기 때문에 적절한 모양으로 패키징되어야 하는데요. 외부의 전원 공급 및 입출력 신호 전류들이 흐를 수 있도록 만들어주어야 하고, 반도체 칩을 외부로부터 보호할 수 있어야 합니다.

# Package공정의 여덟 단계

둥근 웨이퍼가 작은 반도체칩이 되기까지 다양한 과정을 거치게 되는데요. Package공정의 각 과정에 대해 조금 더 알아볼까요?

1) Back Grind

FAB작업이 완료된 두꺼운 웨이퍼를 얇은 다이아몬드 휠로 연마해 얇은 반도체가 될 수 있도록 만드는 과정입니다.

2) Wafer Saw

다수의 칩으로 되어있는 웨이퍼를 낱개의 칩으로 분리합니다.

3) Die Attach

분리한 칩 중에서 양품으로 선별된 개별 칩을 웨이퍼 상에서 떼어내어 외부와 전기적 연결 단자인 Substrate 기판에 접착합니다.

4) Wire Bond

칩의 단자와 Substrate의 단자를 전기적으로 연결해줍니다.

5) Mold

습기, 열, 물리적 충격 등으로부터 보호하기 위해 열경화성 수지인 EMC로 기판을 감싸줍니다.

6) Marking

레이저를 이용해 제품번호를 각인합니다.

7) Solder Ball Mount

PCB와 Package를 전기적으로 연결할 수 있도록 Substrate에 Solder ball을 부착해 아웃단자를 만들어 주는 과정입니다.

8) Saw Singulation

Substrate를 한 개의 개별 제품으로 분리해주는 과정으로, Package의 마지막 단계입니다.

#Package Test의 세 단계

이렇게 완성된 반도체는 최종적으로 Package Test를 거쳐야 하는데요. DRAM의 패키지 테스트 과정을 예시로 살펴볼까요?

1) DC Test & Burn-in

DC Test는 설계 및 조립공정을 거치면서 발생된 불량을 선별하는 공정이며, Burn-in공정은 극한 조건을 가한 후 테스트를 진행함으로써 불량 가능성이 있는 제품을 사전에 검사하는 것입니다. 이 과정을 통과해야 반도체 칩이 들어가는 전자기기가 오류 없이 작동할 수 있는 신뢰성을 갖게 됩니다.

2) Main Test

DC Test Burn in 을 통과한 제품들은 상온, 저온 공간에서 전기적 특성과 기능을 검사 받습니다. 특히 Main test에서는 반도체분야 국제표준인 JEDEC Spec을 맞추기 위한 까다로운 검사가 진행될 뿐만 아니라, 추가로 고객이 요구한 다양한 환경에 맞추어 테스트를 진행합니다. 이 테스트를 통과해야만 Final Test로 가게 됩니다.

3) Final Test

고온에서 반도체의 전기적 특성과 기능을 검사 받는 과정으로 ‘완벽한 반도체’가 되기 위한 마지막 단계입니다.

* 반도체의 기본재료, 웨이퍼(Wafer) : 모래로부터 실리콘을 추출, 가공과 성형을 통해 완성된 잉곳(결정 기둥)을 얇은 판으로 잘라내는 공정

반도체의 기본 재료인 웨이퍼는 실리콘으로 만들어진다. 실리콘은 모래 속에 많이 들어있어 구하기 쉽고, 비용이 적게 든다. 또 고온에서도 소자가 동작할 수 있고, 전기적 특성이 우수해 주 재료로 사용된다.

웨이퍼 공정은 크게 4단계를 거친다. 먼저, 모래에서 추출한 실리콘을 정제하는 과정이 필요하다. 다음으로 실리콘을 고온을 가열해 얻어진 실리콘 용액으로 실리콘 기둥인 잉곳을 만든다. 가공을 통해 완성된 잉곳을 얇은 형태로 잘라 웨어퍼를 얻는다. 마지막으로 웨이퍼 표면을 평평하게 만드는 CMP(Chemical Mechanical Polishing, 화학적 기계적 연마)공정을 거친다.

* 웨이퍼를 보호하라 ‘산화공정’ : 웨어퍼 표면을 보호하는 산화막을 만드는 공정

CMP 공정 후 웨이퍼는 전기가 통하지 않는 부도체 상태이기 때문에 반도체의 성질을 갖도록 작업이 필요하다. 산화공정은 이어지는 공정에서 발생하는 오염물질이나 화학물질에 의한 불순물로부터 실리콘 표면을 보호하는 산화막(SiO2)을 씌우는 공정이다.

* 반도체 회로를 그려라, 포토공정 : 웨이퍼 위에 반도체 회로를 그려 넣는 공정

필름을 인화지에 새기는 방법과 동일한 포토공정은 필름 역할을 하는 마스크(Mask)를 인화지 역할을 하는 웨이퍼에 얹혀서 현상하는 과정이라고 보면 된다.

먼저 웨이퍼 표면에 빛에 민감한 물질인 감광액을 골고루 바른다. 감광액 막이 형성된 웨이퍼는 인화지와 비슷한 상태가 되었다고 보면 된다. 마스크에는 컴퓨터를 이용해 설계회로를 새겨 넣는데 이 마스크가 필름 역할을 하게 된다. 인화할 준비가 되었다면 노광장비인 스태퍼(Stepper)를 사용하여 웨이퍼에 마스크회로를 그려 넣는다. 노광이란 빛을 선택적으로 조사하는 과정을 일컫는데, 웨이퍼 위에 마스크를 놓고 빛을 쪼아 주면 회로 패턴을 통과한 빛이 웨이퍼에 회로 패턴을 그대로 옮기게 된다. 마지막으로 웨이퍼에 현상액을 뿌리면 감광액이 빛에 따라 노광된 영역이 제거된 양성(Positive)와 노광된 영역만 남은 음성(Negative)으로 나눠져 미세한 전자회로 패턴이 새겨지게 된다.

* 불필요한 것은 가라, 식각공정 : 필요한 회로 패턴을 제외한 나머지 부분을 제거하는 공정

포토공정으로 얻어진 회로패턴을 제외한 부분을 제거하는 식각공정은 가스로 깎아내는 건식과 화학액으로 삭여서 파내는 습식으로 나뉜다. 건식은 습식에 비해 비용이 비싸고 방법이 까다롭지만 최근 반도체 기술변화로 회로선 폭이 미세해져서 건식식각이 확대되고 있다.

* 전기적 특성을 갖게 하는 공정

Diffusion & Thin Film 공정을 통해 웨이퍼가 반도체의 성질을 가질 수 있도록 표면에 불순물 확산, 박막 형성 작업

반도체 칩은 한 개의 회로만으로 이루어 진 게 아니라 빌딩을 올리듯이 여러 개의 회로를 쌓아 만든다. 이런 구조를 형성하기 위해서는 회로 간 구분을 해주고 보호를 해주는 역할을 할 수 있는 매우 얇은 막이 필요한데 이것을 ‘박막(Thin Film)’이라 한다.

또한 웨이퍼 위에 분자 또는 워자 단위의 물질을 입혀 전기적 특성을 갖게 하는 공정을 ‘증착(Deposition)’이라고 한다. 증착은 화학적 기상증착방법(CVD, Chemical Vapor Deposition)과 물리적 기상증착방법(PVD, Physical Vapor Deposition)으로 나뉜다. 화학적 기상증착방법을 이용해 금속막을 씌울 경우 전기가 잘 흘러 소통이 원할하게 할 수 있고, 절연막을 씌울 경우 회로와 회로를 분리해 주는 역할을 한다. 여기에 웨이퍼 내부에 이온 불순물을 집어 넣는 Diffusion(확산) 공정을 통해 부도체인 실리콘 웨이퍼가 전기적 특성을 갖는 반도체가 된다. 물리적 기상증착방법은 금속 박막의 증착에 주로 사용되는데 주로 현재 반도체 공정에서는 화학적 기상증착방법을 사용하고 있다.

* 전기적 특성의 완성, 금속 배선 공정

외부에서 얻어지는 전기적 에너지를 받아 소자들끼리 신호가 섞이지 않고 전달되도록 선을 연결하는 작업

전기가 잘 통하도록 하기 위한 금속을 고를 때에도 몇 가지 조건을 만족해야 한다. 먼저 웨어퍼와 부착성이 좋아야 하고, 전기저항이 낮아 전류를 잘 전달할 수 있어야 하며 다른 화학적 열적 공정에서 금속선 특성이 변화하지 않아야 한다. 이런 조건들을 만족하는 대표적인 금속 배선 재료들은 구리(Cu), 알루미늄(Al), 텅스텐(W)이 있다. 하지만 알루미늄의 경우 실리콘과 만나면 섞이려는 성질이 있어 반도체 웨이퍼의 접합면이 상할 수 있다. 따라서 두 접합면 사이에 베리어 메탈(Barrier Metal)이라 불리는 금속을 넣어 접합면이 상하는 것을 방지한다.

* 불량 테스트, EDS (Electrical Die Sorting)

웨이퍼 상태에서 이뤄지는 TEST로 불량을 선별하는 작업

크게 5단계로 이뤄지는 불량테스트(EDS)는 웨이퍼 상태의 개별 칩들의 전기적 특성을 바탕으로 불량품을 선별하는 과정이다.

1단계는 ET Test & WBI(Electrical Test & Wafer Burn In)으로 ET Test는 트랜지스터, 저항과 같은 소자들에 대한 전기적 특성을 테스트해서 작동여부를 확인하는 과정이다. WBI는 웨이퍼에 열을 가한 후 전압을 가해 제품의 잠재적인 오류를 찾아내는 작업이다.

2단계는 Pre-Laser(Hot/Cold)로 특정온도에서 발생하는 오류를 잡아내는 Test와 전기적 신호를 통해 이상 유무를 판별해 수선이 가능한 칩은 수선공정에서 처리하도록 하는 작업이다.

3단계는 Laser Repair & Post Laser로 Pre-Laser 공정에서 수선이 가능하다고 판단된 칩을 모아 수선하는 공정이다.

4단계인 Tape Laminate & Back Grinding에서 Back Grinding은 웨이퍼 후면을 갈아 칩의 두께를 얇게 해서 교통카드와 같은 IC카드에 조립하기 쉽게 한다. 이 때 공정 중에 발생하는 잔여물로부터 웨이퍼 표면을 보호하는 Tape를 씌우는 것이 Tape Laminate공정이고, Grinding이 끝나면 다시 벗긴다.

5단계 Inking은 불량 칩에 특수 잉크를 찍어 육안으로 불량 칩을 식별 할 수 있도록 하는 공정이다.

* 검은 옷의 정체는? 패키징(Packaging)

외부 전원 공급 및 입출력 신호 전류들과 연결, 칩을 외부 환경으로부터 보호하는 작업

금속 연결공정(Wire Bonding)을 통해 외부 전원과 연결 할 수 있도록 하고, 성형(Mold)공정은 수지(Resin)로 구성된 EMC(Epoxy Molding Compound)에 고온을 가해 젤처럼 만든 뒤 원하는 형태의 틀로 넣고 기판을 감싸주는 공정이다. 이런 공정을 거쳐 검은 옷을 입을 반도체 칩은 완제품 합격시험인 패키지 테스트(Package Test)를 거쳐 최종적인 완제품으로 거듭나게 된다.

출처: https://www.skcareersjournal.com/category/News/SK하이닉스?page=6 [SK채용 공식 블로그]

3. 전공별 키워드

화학/화공

산과 염기

열역학(1,2,3) 법칙

층류와 난류

표면장력과 모세관 현상

레이놀즈 수

베르누이 방정식

이상기체 방정식

반데르발스 힘

플라즈마

엔탈피와 엔트로피

총괄열전달계수

알칸

진공

재료/신소재

탄성, 연성, 소성, 취성, 피로 등

항복강도와 인장강도

Bragg 법칙

격자상수

입자계면

그래핀

Charge trap

Lattice & Basis

전자분극 & 천이

결정구조, 결정계

물리

에너지 밴드

해상도

파장

렌즈

초점심도

파동 함수

흑채와 복사

크리스탈 구조

맥스웰 방정식

도핑

까지입니다. 하이닉스 소식 및 상세 면접 팁은 다음 게시물에서 업로드 드리겠습니다~!!!

'취준시 소소한 팁' 카테고리의 다른 글

SK하이닉스 소개 및 공정 정리 + 면접 팁, 팁 2편_200607 (2) 2020.06.07 002. 내가 미리 알았으면 좋았을 취준시 몇가지 소소한 팁 2_200411_R0 (1) 2020.04.11 001. 내가 미리 알았으면 좋았을 취준시 몇가지 소소한 팁_200411_R0 (3) 2020.04.11